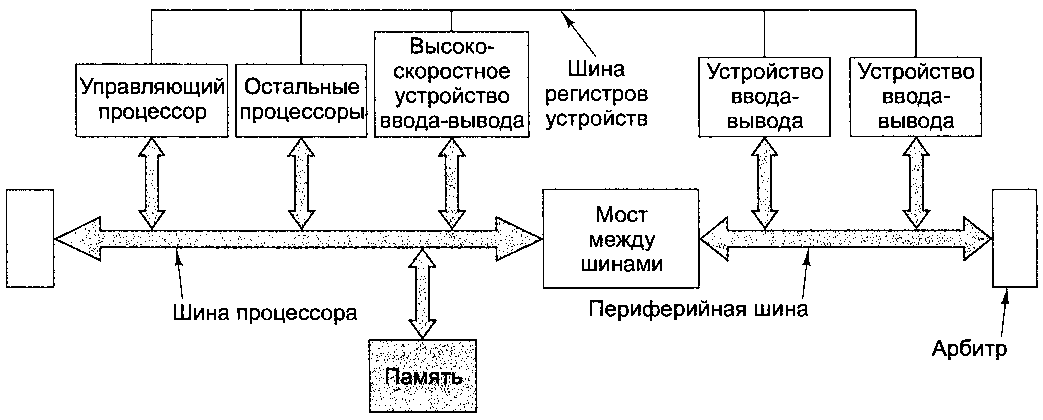

В качестве примера механизма взаимодействия ядер на микросхеме рассмотрим архитектуру CoreConnect компании IBM (рис. 8.10). Она предназначена для объединения ядер в однокристальных гетерогенных мультипроцессорах. Для однокристальных мультипроцессоров CoreConnect выполняет примерно ту же роль, что и шина PCI для Pentium. С другой стороны, в отличие от PCI, архитектура CoreConnect разрабатывалась без расчета на обратную совместимость с устаревшими аппаратными компонентами и протоколами и без оглядки на ограничения, связанные с передачей данных на уровне плат, в частности, с количеством выводов на торцевых соединителях.

Архитектура CoreConnect состоит из трех шин. Шина процессора представляет собой высокоскоростную синхронную конвейеризированную шину с 32, 64 или 128 информационными линиями, работающими на тактовой частоте 66, 133 или 183 МГц. Ее максимальная пропускная способность равна 23,4 Гбит/с (для сравнения, у шины PCI этот показатель составляет 4,2 Гбит/с). Конвейеризация позволяет ядрам запрашивать шину в процессе передачи данных. Кроме того, как и в шине PCI, ядра могут одновременно передавать данные по разным линиям. Шина процессора оптимизирована для передачи коротких блоков данных и призвана обеспечивать взаимодействие между быстрыми ядрами — процессорами, декодерами MPEG-2, высокоскоростными сетями и тому подобными устройствами.

Рис. 8.10. Архитектура CoreConnect компании IBM

Поскольку одной шины процессора на всю микросхему недостаточно, для передачи данных между низкоскоростными устройствами ввода-вывода (UART, таймерами, USB-контроллерами, последовательными устройствами ввода-вывода и т. д.) предусмотрена вторая, периферийная, шина. Она упрощает взаимодействие между 8-, 16- и 32-разрядными периферийными устройствами, используя для этой цели всего несколько сотен вентилей. Периферийная шина также является синхронной, а ее максимальная пропускная способность достигает 300 Мбит/с. Эти две шины соединяются с помощью моста, напоминающего мосты, которыми до недавнего времени соединялись шины PCI и ISA, пока некоторое время назад шина ISA не была вытеснена окончательно.

В архитектуре CoreConnect есть также шина регистров устройств. Это крайне медленная асинхронная шина квитирования, позволяющая процессорам обращаться к регистрам периферийных устройств с целью управления этими устройствами. Передачи по ней проводятся нерегулярно, по несколько байтов.

Сочетание стандартной шины на микросхеме, интерфейса и подобающей инфраструктуры позволяет рассматривать CoreConnect как миниатюрную версию архитектуры PCI, для которой в перспективе можно наладить производство совместимых процессоров и контроллеров. Разница лишь в том, что в мире PCI производители разрабатывают и продают платы продавцам и конечным пользователям. В случае с CoreConnect разработчики ядер предоставляют лицензии на их производство изготовителям бытовой электроники и другим компаниям, которые затем разрабатывают гетерогенные мультипроцессоры на основе собственных и лицензированных ядер. Поскольку для производства больших и сложных микросхем требуются масштабные инвестиции в производственные мощности, в большинстве случаев изготовители бытовой электроники готовят проекты в расчете на заказ микросхем в специализированных компаниях. В настоящее время существуют ядра для процессоров различных типов (ARM, MIPS, PowerPC и т. д.), декодеров MPEG, цифровых процессоров сигналов и всех стандартных контроллеров ввода-вывода.