нашего

сайта:

| Статус нашего сайта: |

|

ICQ Information Center |

ICQ SHOP ICQ SHOP5-значные 6-значные 7-значные 8-значные 9-значные Rippers List  ОПЛАТА ОПЛАТА СТАТЬИ СТАТЬИ СЕКРЕТЫ СЕКРЕТЫ HELP CENTER HELP CENTER OWNED LIST OWNED LIST РОЗЫСК!New! РОЗЫСК!New! ICQ РЕЛИЗЫ ICQ РЕЛИЗЫ Протоколы ICQ Протоколы ICQ LOL ;-) LOL ;-) Настройка компьютера Настройка компьютера Аватарки Аватарки Смайлики Смайлики СОФТ СОФТMail Checkers Bruteforces ICQTeam Soft 8thWonder Soft Other Progs ICQ Patches Miranda ICQ  ФорумАрхив! ФорумАрхив! ВАШ АККАУНТ ВАШ АККАУНТ

РекламаНаш канал:irc.icqinfo.ru |

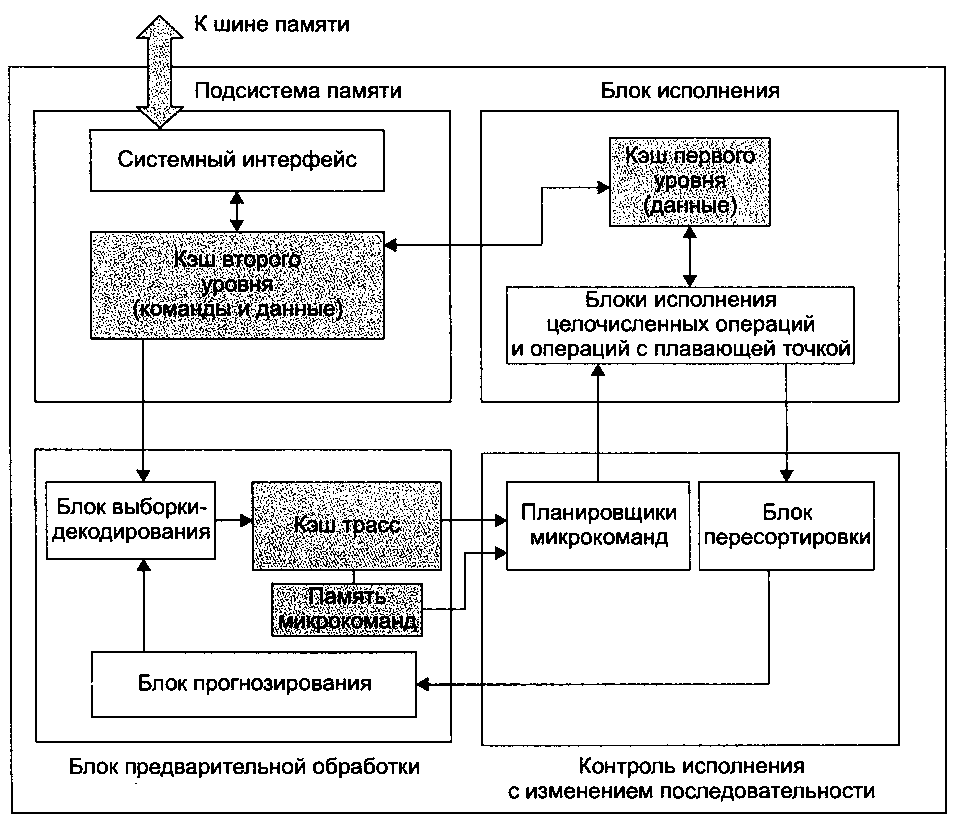

Таненбаум Э.- Архитектура компьютера. стр.247Микроархитектура процессора Pentium 4 На первый взгляд Pentium 4 кажется вполне традиционной CISC-машиной с большим и громоздким набором команд, поддерживающим 8-, 16- и 32-разрядные целочисленные операции, а также 32- и 64-разрядные операции с плавающей точкой. В нем всего 8 доступных регистров, причем ни один из них не повторяет другие. Допустимая длина команд составляет 1-17 байт. В общем, налицо стандартная унаследованная архитектура, которая все делает не так. На самом же деле процессор Pentium 4 основан на современном надежном RISC-ядре с развитой конвейеризацией. Его тактовая частота уже очень высока, а в последующие годы, скорее всего, вырастет еще больше. Удивительно, как инженерам Intel на основе архаичной архитектуры удалось построить процессор, отвечающий всем современным требованиям. Итак, в этом подразделе мы рассмотрим микроархитектуру Pentium 4 и разберемся в принципах ее работы. Обзор микроархитектуры NetBurst Микроархитектура Pentium 4, называемая NetBurst, ознаменовала собой решительный отход от принципов микроархитектуры Р6, использовавшейся в процессорах Pentium Pro, Pentium II и Pentium III. Она дает определенное представление о том, на какой базе продукция Intel будет разрабатываться в течение нескольких ближайших лет. Примерная схема микроархитектуры Pentium 4 изображена на рис. 4.31. В определенной степени она соответствует рисунку 1.8.  Рис. 4.31. Микроархитектура Pentium 4 Pentium 4 состоит из четырех основных блоков: подсистемы памяти, блока предварительной обработки, блока контроля исполнения с изменением последовательности и блока исполнения. Рассмотрим эти блоки по порядку, начиная с верхнего левого и продвигаясь против часовой стрелки. В состав подсистемы памяти входит объединенный кэш второго уровня (L2), а также логика доступа к внешнему ОЗУ по шине памяти. В первом поколении Pentium 4 объем L2 составлял 256 Кбайт; во втором — 512 Кбайт; в третьем — 1 Мбайт. L2 представляет собой 8-входовую ассоциативную кэш-память с 128-байтным строками. Если запрос к кэшу второго уровня не приносит результата, организуются две 64-байтных передачи в основную память, после чего из нее выбираются необходимые блоки. Данный кэш L2 относится к категории кэшей с отложенной записью. Иными словами, новые данные в измененной строке записываются обратно в память лишь после сброса. С кэшем тесно связан блок предварительной выборки (он не показан на рисунке), который пытается перенести данные из основной памяти в L2 еще до того, как эти данные запрошены. Из L2 данные могут на высокой скорости передаваться в другие блоки кэш-памяти. За один цикл может быть выполнена одна операция выборки из L2; так, на тактовой частоте 3 ГГц из L2 в другие кэши теоретически можно передать до 1,5 млрд 64-байтных блоков в секунду — таким образом, пропускная способность становится равной 96 Гбайт/с. Под изображенной на рис. 4.31 подсистемой памяти находится блок предварительной обработки, который выбирает команды из L2 и декодирует их в порядке выполнения команд программы. Каждая команда на уровне ISA разбивается на последовательность RISC-подобных микроопераций. Для упрощения команд блок выборки-декодирования определяет, какие микрооперации необходимы для решения внутренних задач. В более сложных случаях производится поиск последовательности микроопераций в памяти микрокоманд. В любом случае команда уровня ISA процессора Pentium 4 преобразуется в последовательность микроопераций, подлежащих исполнению RISC-ядром микросхемы. Этот механизм позволяет «навести мосты» между устаревшим набором CISC-команд и современным трактом данных RISC. |