нашего

сайта:

| Статус нашего сайта: |

|

ICQ Information Center |

ICQ SHOP ICQ SHOP5-значные 6-значные 7-значные 8-значные 9-значные Rippers List  ОПЛАТА ОПЛАТА СТАТЬИ СТАТЬИ СЕКРЕТЫ СЕКРЕТЫ HELP CENTER HELP CENTER OWNED LIST OWNED LIST РОЗЫСК!New! РОЗЫСК!New! ICQ РЕЛИЗЫ ICQ РЕЛИЗЫ Протоколы ICQ Протоколы ICQ LOL ;-) LOL ;-) Настройка компьютера Настройка компьютера Аватарки Аватарки Смайлики Смайлики СОФТ СОФТMail Checkers Bruteforces ICQTeam Soft 8thWonder Soft Other Progs ICQ Patches Miranda ICQ  ФорумАрхив! ФорумАрхив! ВАШ АККАУНТ ВАШ АККАУНТ

РекламаНаш канал:irc.icqinfo.ru |

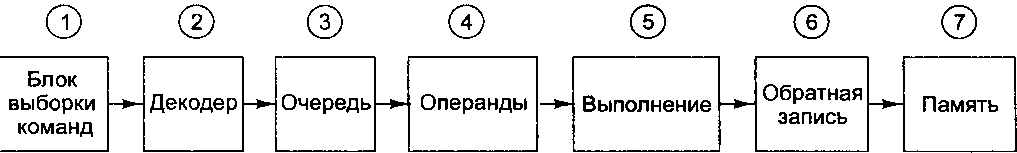

Таненбаум Э.- Архитектура компьютера. стр.230В следующем цикле микрооперация передается в регистр MIR2; выбранные регистры находятся в защелках А и В. Поле АЛУ теперь используется для запуска АЛУ. В следующем цикле поле С запишет результаты обратно в регистры. После этого микрооперация передается в регистр MIR4 и инициирует любую необходимую операцию памяти, используя загруженное значение регистра MAR (или MDR для записи). Нужно обсудить еще один аспект микроархитектуры Mic-4 — микропереходы. Некоторым IJVM-командам нужен условный переход, который осуществляется с помощью бита N. Когда происходит такой переход, конвейер не может продолжать работу. Именно поэтому нам пришлось добавить в микрооперацию бит перехода. Когда в блок формирования очереди поступает микрооперация с таким битом, блок воздерживается от передачи сигнала о получении данных блоку декодирования. В результате машина простаивает до тех пор, пока этот переход не разрешится. Предположительно, некоторые IJVM-команды, не зависящие от этого перехода, могут быть уже переданы в блок декодирования, но не в блок формирования очереди, поскольку он еще не выдал сигнал о получении. Чтобы разобраться в этой путанице и вернуться к нормальной работе, требуется специальное устройство и особые механизмы, но мы не будем рассматривать их в этой книге. Здесь отметим только, что классик, написавший о губительности команд goto, был безусловно прав [55]. Мы начали с микроархитектуры Mic-1 и, пройдя довольно долгий путь, закончили микроархитектурой Mic-4. Аппаратное обеспечение микроархитектуры Mic-1 оказалось очень простым, поскольку практически все управление было реализовано программно. Микроархитектура Mic-4 является конвейеризированной структурой с семью ступенями и более сложным аппаратным обеспечением. Данный конвейер изображен на рис. 4.24. Цифры в кружочках соответствуют компонентам на рис. 4.23. В микроархитектуре Mic-4 поток байтов заранее вызывается из памяти в автоматическом режиме, декодируется в IJVM-команды, которые затем с помощью ПЗУ превращаются в последовательность операций и применяются по назначению. Первые три ступени конвейера при желании можно связать с задающим генератором тракта данных, но работа будет происходить не в каждом цикле. Например, блок выборки команд совершенно точно не смо жет передавать новый код операции блоку декодирования в каждом цикле, поскольку выполнение ЦУМ-команды занимает несколько циклов и очередь быстро переполнится.  Рис. 4.24. Конвейер Mic-4 В каждом цикле значения регистров MIR смещаются, и микрооперация, находящаяся в начале очереди, копируется в регистр MIR1. Затем сигналы управления от всех четырех регистров MIR передаются по тракту данных, вызывая определенные действия. Каждый регистр MIR контролирует отдельную часть тракта данных и, следовательно, разные микрошаги. В данной разработке имеется конвейеризированный процессор. Благодаря этому отдельные шаги становятся очень короткими, а тактовая частота — высокой. Многие процессоры проектируются именно таким образом, особенно те, которым приходится выполнять устаревший набор команд (CISC). Например, процессор Pentium II в некоторых аспектах сходен с микроархитектурой Mic-4, как мы увидим позднее в этой главе. |