нашего

сайта:

| Статус нашего сайта: |

|

ICQ Information Center |

ICQ SHOP ICQ SHOP5-значные 6-значные 7-значные 8-значные 9-значные Rippers List  ОПЛАТА ОПЛАТА СТАТЬИ СТАТЬИ СЕКРЕТЫ СЕКРЕТЫ HELP CENTER HELP CENTER OWNED LIST OWNED LIST РОЗЫСК!New! РОЗЫСК!New! ICQ РЕЛИЗЫ ICQ РЕЛИЗЫ Протоколы ICQ Протоколы ICQ LOL ;-) LOL ;-) Настройка компьютера Настройка компьютера Аватарки Аватарки Смайлики Смайлики СОФТ СОФТMail Checkers Bruteforces ICQTeam Soft 8thWonder Soft Other Progs ICQ Patches Miranda ICQ  ФорумАрхив! ФорумАрхив! ВАШ АККАУНТ ВАШ АККАУНТ

РекламаНаш канал:irc.icqinfo.ru |

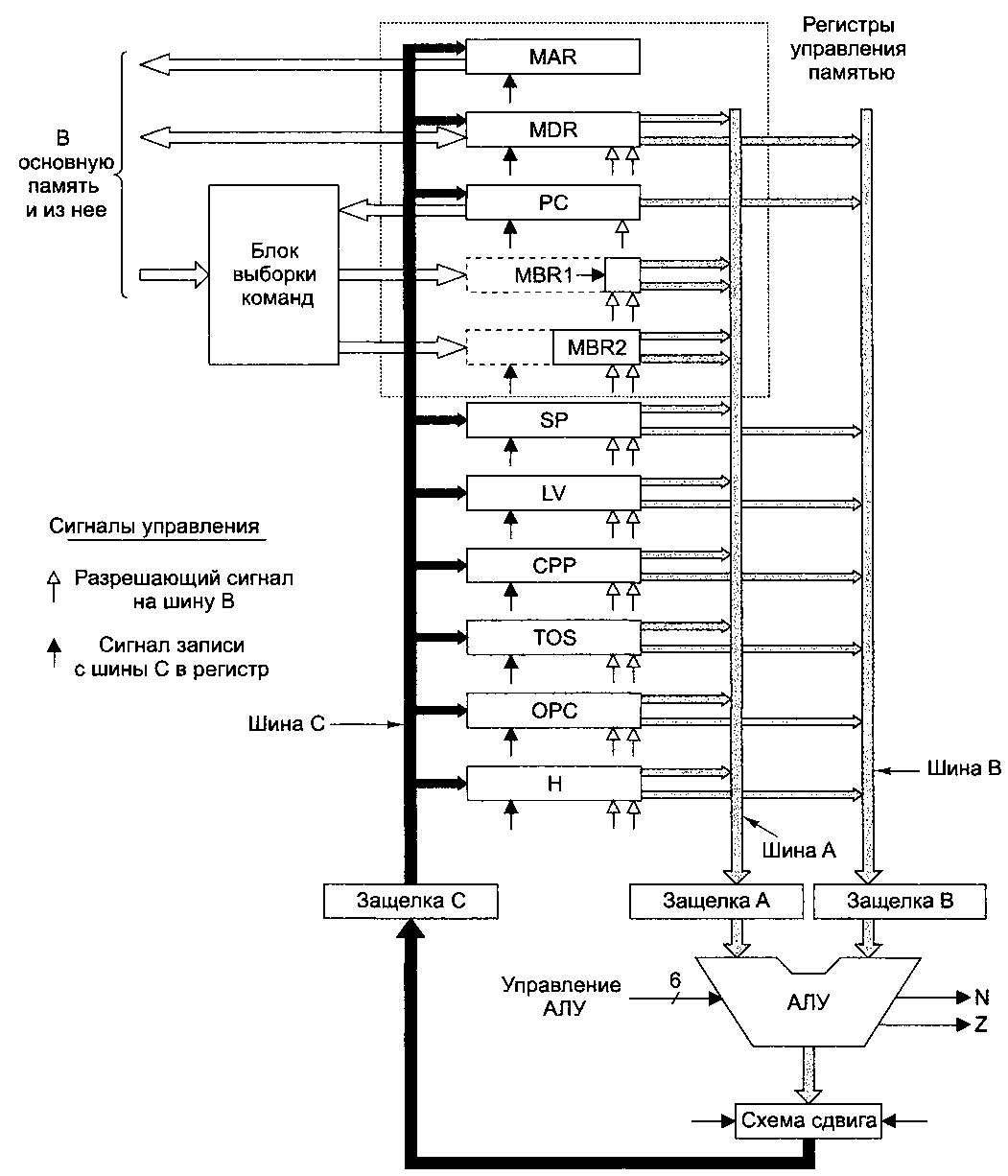

Таненбаум Э.- Архитектура компьютера. стр.225Конвейерная конструкция — микроархитектура Mic-3 Очевидно, что Mic-2 — это усовершенствованная микроархитектура Mic-1. Она работает быстрее и требует меньше управляющей памяти, хотя стоимость блока выборки команд несомненно превышает сумму, выигранную за счет сокращения объема управляющей памяти. Таким образом, машина Mic-2 работает значительно быстрее при некотором увеличении стоимости. Давайте посмотрим, можно ли еще больше повысить скорость. А что, если попробовать уменьшить время цикла? В значительной степени время цикла определяется базовой технологией. Чем меньше транзисторы и физическое расстояние между ними, тем быстрее может работать задающий генератор. В технологии, которую мы рассматриваем, время, затрачиваемое на прохождение через тракт данных, фиксировано (по крайней мере, с нашей точки зрения). Тем не менее у нас есть некоторая свобода действий и далее мы используем ее в полной мере. Еще один вариант усовершенствования — увеличить степень параллелизма. На данный момент микроархитектура Mic-2 выполняет большинство операций последовательно. Она помещает значения регистров на шины, ждет, пока АЛУ и схема сдвига их обработают, а затем записывает результаты обратно в регистры. Если не учитывать работу блока выборки команд, никакого параллелизма здесь нет. Внедрение дополнительных механизмов параллельной обработки сулит значительные преимущества. Как уже отмечалось, длительность цикла определяется временем, необходимым для прохождения сигнала через тракт данных. На рис. 4.2 показано распределение этой задержки между различными компонентами во время каждого цикла. Цикл тракта данных объединяет три основные составляющие: 1. Время, которое требуется на передачу значений выбранных регистров на шины А и В. 2. Время, которое требуется на работу АЛУ и схемы сдвига. 3. Время, которое требуется на передачу полученных значений обратно в регистры и сохранение этих значений. На рис. 4.21 показана новая 3-шинная архитектура с блоком выборки команд и тремя дополнительными защелками (регистрами), каждая из которых расположена в середине каждой шины. Эти регистры записываются в каждом цикле. Они делят тракт данных на отдельные части, которые могут функционировать независимо друг от друга. Мы будем называть такую архитектуру конвейерной моделью, или Міс-3.  Рис. 4.21. Тракт данных с тремя шинами в микроархитектуре Міс-3 Зачем нужны целых три дополнительных регистра? Ведь теперь для прохождения сигнала через тракт данных требуется 3 цикла: один для загрузки регистров А и В, второй для запуска АЛУ и схемы сдвига, а также загрузки регистра С, третий для сохранения значения регистра-защелки С обратно в нужных регистрах. Мы что, ненормальные? (Подсказка: нет.) Существует целых две причины введения дополнительных регистров: 1. Мы можем повысить тактовую частоту, поскольку максимальная задержка теперь стала меньше. 2. Во время каждого цикла мы можем использовать все части тракта данных. После разбиения тракта данных на три части максимальная задержка прохождения сигнала уменьшается, в результате тактовая частота может повышаться. Будем считать, что, если разбить цикл тракта данных на три примерно равных интервала, тактовая частота увеличится втрое. (На самом деле это не так, поскольку мы добавили в тракт данных еще два регистра, но в первом приближении это допустимо.) |