нашего

сайта:

| Статус нашего сайта: |

|

ICQ Information Center |

ICQ SHOP ICQ SHOP5-значные 6-значные 7-значные 8-значные 9-значные Rippers List  ОПЛАТА ОПЛАТА СТАТЬИ СТАТЬИ СЕКРЕТЫ СЕКРЕТЫ HELP CENTER HELP CENTER OWNED LIST OWNED LIST РОЗЫСК!New! РОЗЫСК!New! ICQ РЕЛИЗЫ ICQ РЕЛИЗЫ Протоколы ICQ Протоколы ICQ LOL ;-) LOL ;-) Настройка компьютера Настройка компьютера Аватарки Аватарки Смайлики Смайлики СОФТ СОФТMail Checkers Bruteforces ICQTeam Soft 8thWonder Soft Other Progs ICQ Patches Miranda ICQ  ФорумАрхив! ФорумАрхив! ВАШ АККАУНТ ВАШ АККАУНТ

РекламаНаш канал:irc.icqinfo.ru |

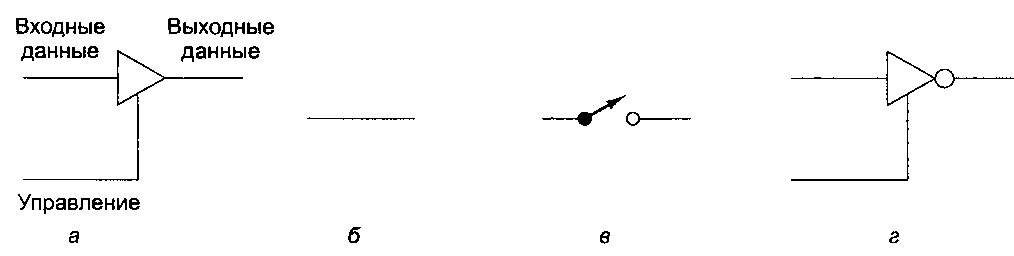

Таненбаум Э.- Архитектура компьютера. стр.137К счастью, такие переключатели существуют. На рис. 3.29, а показано символическое изображение так называемого буферного элемента без инверсии. Он содержит входную линию для данных, выходную линию для данных и входную линию для управления. Когда управляющий вход равен 1, буферный элемент работает как проводник (рис. 3.29, б). Когда управляющий вход равен 0, буферный элемент работает как изолятор (рис. 3.29, в), как будто кто-то отрезает выход для данных от остальной части схемы кусачками. Соединение может быть восстановлено за несколько наносекунд, если сделать сигнал управления равным 1.  Рис. 3.29. Буферный элемент без инверсии (а); представление буферного элемента без инверсии, когда сигнал управления равен 1 (б); представление буферного элемента без инверсии, когда сигнал управления равен 0 (в); буферный элемент с инверсией (г) На рис. 3.29, г показан буферный элемент с инверсией, который действует как обычный инвертор, когда сигнал управления равен 1, и отделяет выход от остальной части схемы, когда сигнал управления равен 0. Оба буферных элемента представляют собой устройства с тремя состояниями, поскольку могут выдавать нулевой сигнал, единичный сигнал или вообще не выдавать никакого сигнала (случай разомкнутой цепи). Буферные элементы, кроме того, усиливают сигналы, поэтому они могут справляться с большим количеством сигналов одновременно. Иногда они используются в схемах именно в качестве усилителей. Теперь вам уже должно быть понятно, для чего нужны три буферных элемента без инверсии на линиях вывода данных. Когда сигналы CS, RD и ОЕ равны 1, сигнал разрешения выдачи выходных данных также равен 1, в результате запускаются буферные элементы и слово помещается на выходные линии. Когда один из сигналов CS, RD и ОЕ равен 0, выходы отсоединяются от остальной части схемы. Микросхемы памяти Преимущество памяти, изображенной на рис. 3.28, состоит в том, что подобная структура применима при разработке памяти большого объема. На рисунке показана схема 4x3 (для четырех слов по 3 бита каждое). Чтобы расширить ее до размеров 4x8, нужно добавить еще 5 колонок триггеров по 4 триггера в каждой, а также 5 входных и 5 выходных линий. Чтобы перейти от схемы 4 х 3 к схеме 8x3, требуется добавить еще четыре ряда триггеров по три триггера в каждом, а также адресную линию А2. При такой структуре число слов в памяти должно быть степенью двойки для максимальной эффективности, а число битов в слове может быть любым. Технология изготовления интегральных схем идеально соответствует регулярной структуре микросхем памяти. С развитием технологии число битов, которое можно вместить в одной микросхеме, постоянно растет, обычно в два раза каждые 18 месяцев (закон Мура). С появлением больших микросхем маленькие микросхемы не всегда сразу устаревают, поскольку всегда существует компромисс между емкостью, быстродействием, мощностью, ценой и удобством сопряжения. Обычно самые большие современные микросхемы пользуются огромным спросом и, следовательно, стоят гораздо дороже в расчете за 1 бит, чем микросхемы небольшого размера. |